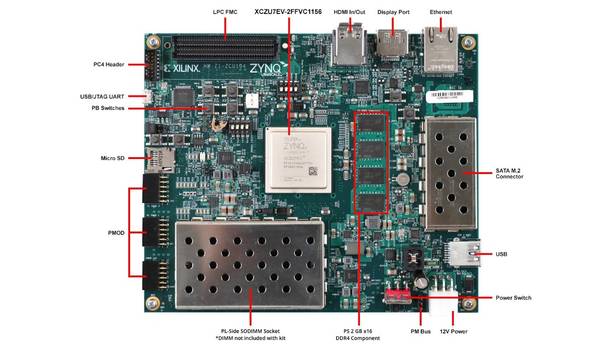

Zynq UltraScale+ MPSoC ZCU104

Обзор Железо Документация Софт и IP Обучение и поддержка

|

|||||||||||||||||||||||||||||||||||||||||||||||

| Параметр | Значение | |

| Системных логических ячеек | 504 |  |

| Памяти | 38 Мб | |

| DSP секций | 1728 | |

| Видео кодек | 1 | |

| Максимальное число в/в | 464 |

Что установлено на плате?

Конфигурация

|

Память

|

Настройка

|

Расширение

|

Сетевые интерфейсы

|

Видео интерфейсы

|

Тактирование

|

Питание

|

Комплект поставки

|

ZCU104 Evaluation Board |

Доступ к полноценной Vivado® Design Suite: Design Edition Лицензия привязана к кристаллу и компьютеру XCZU7EV MPSoC FPGA с обновлением на 1 год |

Кабель Ethernet |

Доступ к SDSoC |

1080p60 USB3 Camera |

Блок питания |

USB 3.0 Hub |

Документация

Полный список документации доступен на сайте производителя

Софт и IP

| SDSoC | Среда для разработки на C/C++ | Лицензия привязана к плате и кристаллу Zynq Ultrascale+ MPSoC |

| Vivado Design Suite Design Edition | Xilinx Vivado Design Suite - Основная среда разработки на ПЛИС и СнК компании Xilinx. |

Доступ к полноценной Vivado® Design Suite: Design Edition Лицензия привязана к плате и кристаллу XCZU7EV MPSoC FPGA, с возможностью обновления в течение одного года |

| Xilinx SDK | Полный набор инструментов для разработки встроенного программного обеспечения и отладки платформ Xilinx | Бесплатно |

| PetaLinux Tools | Настройка, сборка и развертывание операционной системы Linux на платформах Xilinx | Бесплатно |

| Memory Interface Generator (MIG) | MIG это бесплатное IP для создания контроллера памяти на FPGA Xilinx | Включена |

Обучение и поддержка

По вопросам обучения - сертифицированный тренинг центр Xilinx - сайт тренинг центра

По техническим вопросам - Коробков Михаил m.korobkov@inline-ctc.ru (инженер по применению Xilinx)